#### SEMICONDUCTOR TECHNICAL DATA

# Preliminary Information

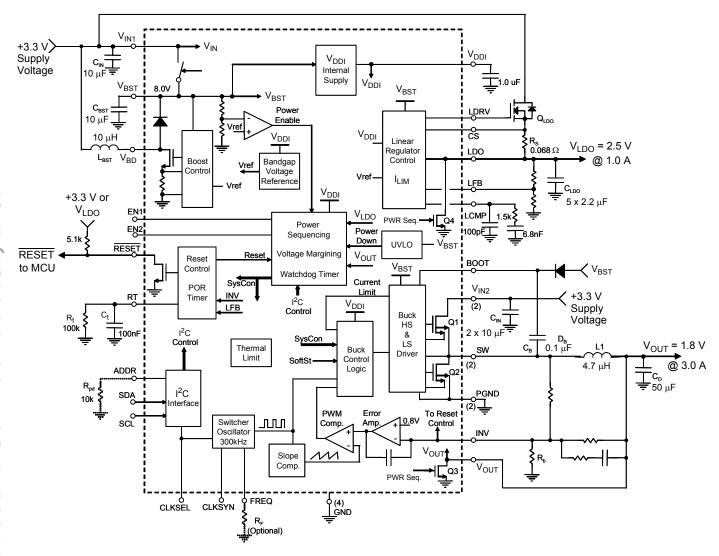

# 3.0 A Switch-Mode Power Supply with Linear Regulator

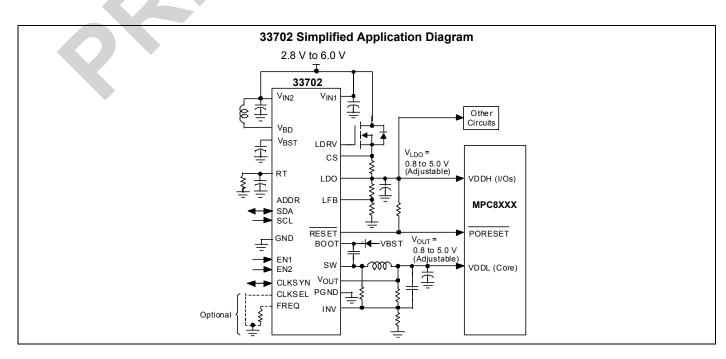

The 33702 provides the means to efficiently supply the Power QUICC™ I, II, and other families of Motorola microprocessors and DSPs. The 33702 incorporates a high-performance switching regulator, providing the direct supply for the microprocessor's core, and a low dropout (LDO) linear regulator control circuit providing the microprocessor I/O and bus voltage.

The switching regulator is a high-efficiency synchronous buck regulator with integrated 50 m $\Omega$  N-channel power MOSFETs to provide protection features and to allow space-efficient, compact design.

The 33702 incorporates many advanced features; e.g., precisely maintained up/down power sequencing, ensuring the proper operation and protection of the CPU and power system.

#### **Features**

- Operating Voltage: 2.8 V to 6.0 V

- High-Accuracy Output Voltages

- Fast Transient Response

- Switcher Output Current Up to 3.0 A

- Undervoltage Lockout

- Power Sequencing

- Programmable Watchdog Timer

- Voltage Margining via I<sup>2</sup>C™ Bus

- Overcurrent Protection

- Reset with Programmable Power-ON Delay

- **Enable Inputs**

I<sup>2</sup>C is a trademark of Phillips Corporation.

# 33702

## **POWER SUPPLY** INTEGRATED CIRCUIT

#### **ORDERING INFORMATION**

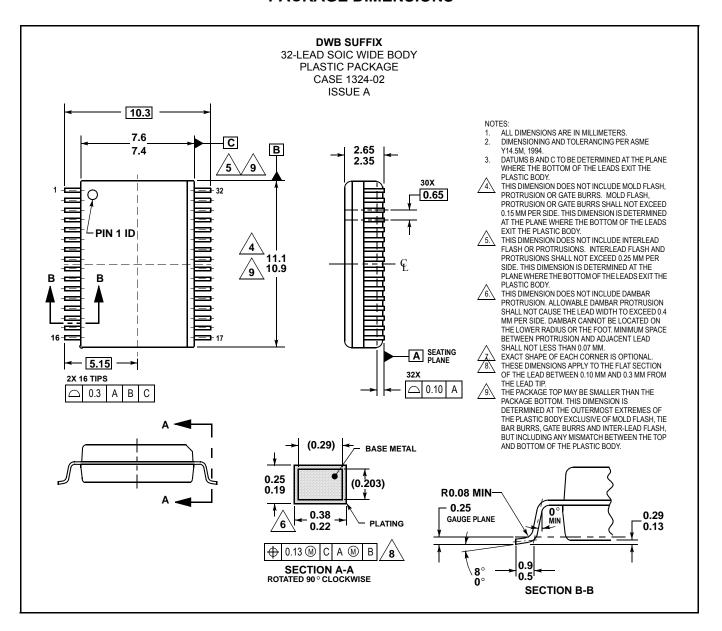

| Device        | Temperature<br>Range (T <sub>A</sub> ) | Package  |

|---------------|----------------------------------------|----------|

| PC33702DWB/R2 | -40 to 85°C                            | 32 SOICW |

This document contains information on a product under development. Motorola reserves the right to change or discontinue this product without notice.

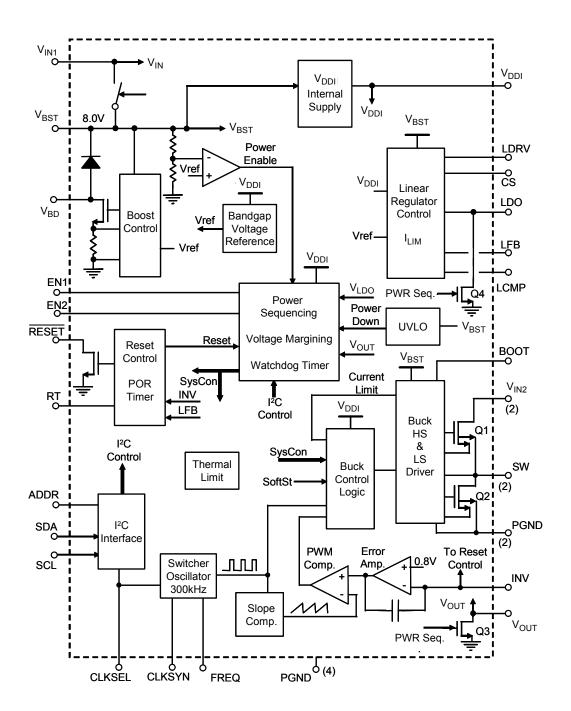

Figure 1. 33702 Simplified Block Diagram

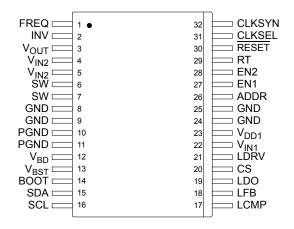

#### PIN FUNCTION DESCRIPTION

| Pin            | Pin Name         | Formal Name          | Definition                                                                                                                                                                                                                                                                                                                    |

|----------------|------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1              | FREQ             | Oscillator Frequency | This selection switcher pin can be adjusted by connecting external resistor $R_F$ to the FREQ pin. The default switching frequency (FREQ pin left open or tied to $V_{DDI}$ ) is set to 300 kHz.                                                                                                                              |

| 2              | INV              | Inverting Input      | Buck Controller Error Amplifier inverting input.                                                                                                                                                                                                                                                                              |

| 3              | V <sub>OUT</sub> | Output Voltage       | Output voltage of the buck converter. Input pin of the switching regulator power sequence control circuit.                                                                                                                                                                                                                    |

| 4, 5           | V <sub>IN2</sub> | Input Voltage 2      | Buck regulator power input. Drain of the high-side power MOSFET.                                                                                                                                                                                                                                                              |

| 6, 7           | SW               | Switch               | Buck regulator switching node. This pin is connected to the inductor.                                                                                                                                                                                                                                                         |

| 8, 9<br>24, 25 | GND              | Ground               | Analog ground of the IC, thermal heatsinking.                                                                                                                                                                                                                                                                                 |

| 10, 11         | PGND             | Power Ground         | Buck regulator power ground.                                                                                                                                                                                                                                                                                                  |

| 12             | V <sub>BD</sub>  | Boost Drain          | Drain of the internal boost regulator power MOSFET.                                                                                                                                                                                                                                                                           |

| 13             | V <sub>BST</sub> | Boost Voltage        | Internal boost regulator output voltage. The internal boost regulator provides a 20 mA output current to supply the drive circuits for the integrated power MOSFETs and the external N-channel power MOSFET of the linear regulator. The voltage at the V <sub>BST</sub> pin is 8.0 V nominal.                                |

| 14             | воот             | Bootstrap            | Bootstrap capacitor input.                                                                                                                                                                                                                                                                                                    |

| 15             | SDA              | Serial Data          | I <sup>2</sup> C bus pin. Serial data.                                                                                                                                                                                                                                                                                        |

| 16             | SCL              | Serial Clock         | I <sup>2</sup> C bus pin. Serial clock.                                                                                                                                                                                                                                                                                       |

| 17             | LCMP             | Linear Compensation  | Linear regulator compensation pin.                                                                                                                                                                                                                                                                                            |

| 18             | LFB              | Linear Feedback      | Linear regulator feedback pin.                                                                                                                                                                                                                                                                                                |

| 19             | LDO              | Linear Regulator     | Input pin of the linear regulator power sequence control circuit.                                                                                                                                                                                                                                                             |

| 20             | CS               | Current Sense        | Current sense pin of the LDO. Overcurrent protection of the linear regulator external power MOSFET. The voltage drop over the LDO current sense resistor $R_{\rm S}$ is sensed between the CS and LDO pins. The LDO current limit can be adjusted by selecting the proper value of the current sensing resistor $R_{\rm S}$ . |

| 21             | LDRV             | Linear Drive         | LDO gate drive of the external pass N-channel MOSFET.                                                                                                                                                                                                                                                                         |

| 22             | V <sub>IN1</sub> | Input Voltage 1      | The input supply pin for the integrated circuit. The internal circuits of the IC are supplied through this pin.                                                                                                                                                                                                               |

### **PIN FUNCTION DESCRIPTION (continued)**

| Pin | Pin Name         | Formal Name           | Definition                                                                                                                                                                                                                      |

|-----|------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23  | V <sub>DDI</sub> | Power Supply          | Internal supply voltage.                                                                                                                                                                                                        |

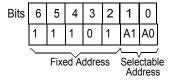

| 26  | ADDR             | Address               | $\mbox{I}^2\mbox{C}$ address selection. This pin can be either left open, tied to $\mbox{V}_{DDI},$ or grounded through a 10 k $\Omega$ resistor.                                                                               |

| 27  | EN1              | Enable 1              | Enable 1 Input. The combination of the logic state of the Enable 1 and Enable 2 inputs determine operation mode and type of power sequencing of the IC.                                                                         |

| 28  | EN2              | Enable 2              | Enable 2 Input. The combination of the logic state of the Enable 1 and Enable 2 inputs determine operation mode and type of power sequencing of the IC.                                                                         |

| 29  | RT               | Reset Timer           | This pin allows programming the Power-ON Reset delay by means of an external RC network.                                                                                                                                        |

| 30  | RESET            | Reset Overbar         | The Reset Control circuit monitors both the switching regulator and the LDO feedback voltages. It is an open drain output and has to be pulled up to some supply voltage (e.g., the output of the LDO) by an external resistor. |

| 31  | CLKSEL           | Clock Selection       | This pin sets the CLKSYN pin either as an oscillator output or synchronization input pin. The CLKSEL pin is also used for the I <sup>2</sup> C address selection.                                                               |

| 32  | CLKSYN           | Clock Synchronization | Oscillator output/synchronization input pin.                                                                                                                                                                                    |

#### **MAXIMUM RATINGS**

All voltages are with respect to ground unless otherwise noted.

| Rating                                                  | Symbol                              | Value       | Unit |

|---------------------------------------------------------|-------------------------------------|-------------|------|

| Supply Voltage                                          | V <sub>IN1</sub> , V <sub>IN2</sub> | -0.3 to 7.0 | V    |

| Switching Node                                          | SW                                  | -1.0 to 7.0 | V    |

| Buck Regulator Bootstrap Input (BOOT - SW)              | BOOT                                | -0.3 to 8.5 | V    |

| Boost Regulator Output                                  | V <sub>BST</sub>                    | -0.3 to 8.5 | V    |

| Boost Regulator Drain                                   | V <sub>BD</sub>                     | -0.3 to 9.5 | V    |

| RESET Drain Voltage                                     | RESET                               | -0.3 to 7.0 | V    |

| Enable Pins (EN1, EN2)                                  | -                                   | -0.3 to 7.0 | V    |

| Logic Pins (SDA, SCL, CLKSYN)                           | -                                   | -0.3 to 7.0 | V    |

| Analog Pins (INV, V <sub>OUT</sub> , RESET)             | -                                   | -0.3 to 7.0 | V    |

| Analog Pins (LDRV <sub>,</sub> LFB, LDO, LCMP, CS)      | -                                   | -0.3 to 8.5 | V    |

| Analog Pins (CLKSEL, ADDR, RT, FREQ, V <sub>DDI</sub> ) | -                                   | -0.3 to 3.6 | V    |

| ESD Voltage                                             |                                     |             | V    |

| Human Body Model (Note 1)                               | V <sub>ESD1</sub>                   | ±2000       |      |

| Machine Model (Note 2)                                  | V <sub>ESD2</sub>                   | ±200        |      |

| Storage Temperature                                     | T <sub>STG</sub>                    | -65 to 150  | °C   |

| Power Dissipation (T <sub>A</sub> = 85°C) (Note 3)      | P <sub>D</sub>                      | TBD         | W    |

| Lead Soldering Temperature (Note 4)                     | T <sub>SOLDER</sub>                 | 260         | °C   |

| Maximum Junction Temperature                            | T <sub>JMAX</sub>                   | 125         | °C   |

| Thermal Resistance, Junction to Ambient (Note 5)        | $R_{	heta JA}$                      | 68          | °C/W |

| Thermal Resistance, Junction to Base (Note 6)           | $R_{	heta JB}$                      | 18          | °C/W |

#### **OPERATING CONDITIONS**

| Supply Voltage (V <sub>IN1</sub> , V <sub>IN2</sub> ) | V <sub>IN1</sub> , V <sub>IN2</sub> | 2.8 to 6.0 | V  |

|-------------------------------------------------------|-------------------------------------|------------|----|

| Operational Package Temperature (Ambient Temperature) | T <sub>A</sub>                      | -40 to 85  | °C |

#### Notes

- 1. ESD1 testing is performed in accordance with the Human Body Model ( $C_{ZAP}$ =100 pF,  $R_{ZAP}$ =1500  $\Omega$ ).

- 2. ESD2 testing is performed in accordance with the Machine Model ( $C_{ZAP}$ =200 pF,  $R_{ZAP}$ =0  $\Omega$ ).

- 3. Maximum power dissipation at indicated junction temperature.

- 4. Lead soldering temperature limit is for 10 seconds maximum duration. Contact Motorola Sales Office for device immersion soldering time/ temperature limits.

- 5. Thermal resistance measured in accordance with EIA/JESD51-2.

- 6. Theoretical thermal resistance from the die junction to the exposed pins.

#### STATIC ELECTRICAL CHARACTERISTICS

Characteristics noted under conditions  $-40^{\circ}\text{C} \le T_{\text{J}} \le 125^{\circ}\text{C}$  unless otherwise noted. Input voltages  $V_{\text{IN1}} = V_{\text{IN2}} = 3.3 \text{ V}$  using the typical application circuit (see Figure 20) unless otherwise noted.

| Characteristic                                                                                                                                                                               | Symbol                | Min   | Тур      | Max      | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------|----------|----------|------|

| GENERAL                                                                                                                                                                                      |                       |       |          |          |      |

| Operating Voltage Range (V <sub>IN1</sub> , V <sub>IN2</sub> )                                                                                                                               | V <sub>IN</sub>       | 2.8   | _        | 6.0      | V    |

| Start-Up Voltage Threshold (Boost Switching)                                                                                                                                                 | V <sub>ST</sub>       | -     | 1.6      | 1.8      | V    |

| V <sub>BST</sub> Undervoltage Lockout                                                                                                                                                        | V <sub>BST_UVLO</sub> | -     | 6.0      | _        | V    |

| Input DC Supply Current (Normal Operation Mode, Enabled)                                                                                                                                     | I <sub>IN</sub>       | -     | 60       | -        | mA   |

| V <sub>IN1</sub> Pin Input Supply Current (EN1 = EN2 = 0)                                                                                                                                    | I <sub>IN1</sub>      | -     | 9.0      | _        | mA   |

| V <sub>IN2</sub> Pin Input Leakage Current (EN1 = EN2 = 0)                                                                                                                                   | I <sub>IN2</sub>      | -     | TBD      | -        | μΑ   |

| V <sub>DDI</sub> Internal Supply Voltage                                                                                                                                                     | V <sub>DDI</sub>      | 3.0   | -        | 3.3      | V    |

| V <sub>DDI</sub> Maximum Output Current                                                                                                                                                      | I <sub>DDI</sub>      | -     | TBD      | _        | μА   |

| BUCK CONVERTER                                                                                                                                                                               |                       |       | <u> </u> | <u> </u> | I    |

| Buck Converter Output Voltage Range $I_{VOUT}$ = 30 mA to 3.0 A, $V_{IN1}$ = $V_{IN2}$ = 2.8 V to 6.0 V                                                                                      | V <sub>OUT</sub>      | 0.8   | _        | 5.0      | V    |

| Buck Converter Feedback Voltage $I_{VOUT} = 30 \text{ mA to } 3.0 \text{ A, V}_{IN1} = V_{IN2} = 2.8 \text{ V to } 6.0 \text{ V. No R}_{B} \text{ Resistor.}$ Includes Load Regulation Error | V <sub>INV</sub>      | 0.784 | 0.8      | 0.816    | V    |

| Buck Converter Voltage Margining Step                                                                                                                                                        | V <sub>MVO</sub>      | -     | 1.0      | -        | %    |

| Buck Converter Line Regulation $V_{\text{IN1}} = V_{\text{IN2}} = 2.8 \text{ V to } 6.0 \text{ V, } I_{\text{VOUT}} = 3.0 \text{ A}$                                                         | REG <sub>LNVO</sub>   | -1.0  | _        | 1.0      | %    |

| Buck Converter Load Regulation  I <sub>VOUT</sub> = 30 mA to 3.0 A                                                                                                                           | REG <sub>LDVO</sub>   | -1.0  | _        | 1.0      | %    |

| V <sub>OUT</sub> Input Leakage Current<br>V <sub>OUT</sub> = 5.0 V                                                                                                                           | I <sub>VOUTLK</sub>   | -     | TBD      | _        | μА   |

| High-Side Power MOSFET Q1 $R_{DS(ON)}$<br>$I_D$ = 1.0 A, $T_A$ = 25°C, $V_{BST}$ = 8.0 V                                                                                                     | R <sub>DS(ON)</sub>   | _     | _        | 50       | mΩ   |

| Low-Side Power MOSFET Q2 $R_{DS(ON)}$<br>$I_D$ = 1.0 A, $T_A$ = 25°C, $V_{BST}$ = 8.0 V                                                                                                      | R <sub>DS(ON)</sub>   | -     | _        | 50       | mΩ   |

| Buck Converter Peak Current Limit (High Level)                                                                                                                                               | I <sub>H_LIM</sub>    | 3.4   | 4.5      | 6.0      | Α    |

| Buck Converter Valley Current Limit (Low Level)                                                                                                                                              | I <sub>L_LIM</sub>    | 1.7   | 2.25     | 3.0      | Α    |

| $V_{OUT}$ Pull-Down MOSFET Q3 Current Limit<br>$T_A = 25$ °C, $V_{BST} = 8.0 \text{ V}$                                                                                                      | I <sub>Q3_LIM</sub>   | -     | 2.0      | _        | А    |

| V <sub>OUT</sub> Pull-Down MOSFET Q3 R <sub>DS(ON)</sub> I <sub>D</sub> = 1.0 A, T <sub>A</sub> = 25°C, V <sub>BST</sub> = 8.0 V                                                             | R <sub>DS(ON)</sub>   | _     | _        | 1.0      | Ω    |

| Thermal Shutdown (Switcher, V <sub>OUT</sub> FET)                                                                                                                                            | T <sub>SD</sub>       | 150   | 170      | 190      | °C   |

|                                                                                                                                                                                              | T                     |       | 45       |          | 0.0  |

°C

Thermal Shutdown Hysteresis

#### STATIC ELECTRICAL CHARACTERISTICS (continued)

Characteristics noted under conditions -40°C  $\leq$  T<sub>J</sub> $\leq$  125°C unless otherwise noted. Input voltages V<sub>IN1</sub> = V<sub>IN2</sub> = 3.3 V using the typical application circuit (see Figure 20) unless otherwise noted.

| Characteristic                                                                                                   | Symbol              | Min  | Тур  | Max | Unit |

|------------------------------------------------------------------------------------------------------------------|---------------------|------|------|-----|------|

| ERROR AMPLIFIER (BUCK CONVERTER)                                                                                 |                     |      |      |     |      |

| Input Impedance (Note 7)                                                                                         | R <sub>IN</sub>     | _    | 500  | -   | kΩ   |

| Output Impedance (Note 7)                                                                                        | R <sub>OUT</sub>    | _    | 150  | _   | Ω    |

| DC Open Loop Gain (Note 7)                                                                                       | A <sub>VOL</sub>    | _    | 80   | _   | dB   |

| Gain Bandwidth Product (Note 7)                                                                                  | GBW                 | _    | 35   | -   | MHz  |

| Slew Rate (Note 7)                                                                                               | SR                  | _    | 200  | _   | V/μs |

| Output Voltage Swing – High Level $V_{\text{IN1}} \ge 3.3 \text{ V}, I_{\text{OEA}} = -1.0 \text{ mA (Note 7)}$  | V <sub>EA_OH</sub>  | _    | 2.0  | _   | V    |

| Output Voltage Swing – Low Level  I <sub>OEA</sub> = -1.0 mA (Note 7)                                            | V <sub>EA_OL</sub>  | _    | 0.4  | _   | V    |

| Slope Compensation Ramp (Note 7)                                                                                 | V <sub>SCRamp</sub> | _    | 0.6  | _   | V    |

| OSCILLATOR                                                                                                       |                     |      |      | •   | •    |

| Oscillator Low Level Output Voltage (Pin CLKSYN), CLKSEL Open                                                    | V <sub>osc_ol</sub> | _    | _    | 0.4 | V    |

| Oscillator High Level Output Voltage (Pin CLKSYN), CLKSEL Open                                                   | V <sub>OSC_OH</sub> | 3.0  | _    | -   | V    |

| Oscillator Input Voltage Threshold (Pin CLKSYN), CLKSEL Grounded                                                 | V <sub>OSC_IH</sub> | 1.2  | 1.6  | 2.0 | V    |

| Oscillator Frequency Adjusting Reference Voltage (FREQ)                                                          | V <sub>FREQ</sub>   | -    | 1.29 | -   | V    |

| Oscillator Frequency Adjusting Resistor Range                                                                    | R <sub>FREQ</sub>   | 100  | _    | 200 | kΩ   |

| BOOST REGULATOR                                                                                                  | -                   |      | •    | •   |      |

| Boost Regulator Output Voltage<br>I <sub>BST</sub> = 20 mA, V <sub>IN1</sub> = V <sub>IN2</sub> = 2.8 V to 6.0 V | V <sub>BST</sub>    | 7.5  | 8.0  | 8.5 | V    |

| Boost Regulator Start-Up Voltage                                                                                 | V <sub>IN_BSU</sub> | -    | 1.6  | 1.8 | V    |

| Boost Regulator Peak Current Limit (Power FET Peak Current)                                                      | I <sub>P_BD</sub>   | 0.75 | 1.0  | 1.5 | Α    |

| Boost Regulator Power FET Valley Current Limit (Low Level)                                                       | I <sub>L_BD</sub>   | 450  | 600  | 800 | mA   |

| Boost Power FET R <sub>DS(ON)</sub> $I_{BD} = 1.0 \text{ A, T}_{A} = 25^{\circ}\text{C}$                         | R <sub>DS(ON)</sub> | _    | 150  | 400 | mΩ   |

| Boost Regulator Recommended Output Capacitor                                                                     | C <sub>BST</sub>    | -    | 10   | -   | μF   |

| Boost Regulator Recommended Output Capacitor Maximum ESR                                                         | ESR <sub>CBST</sub> | -    | 100  | -   | mΩ   |

#### Notes

7. Design information only. It is not production tested.

### STATIC ELECTRICAL CHARACTERISTICS (continued)

Characteristics noted under conditions -40°C  $\leq$  T<sub>J</sub> $\leq$  125°C unless otherwise noted. Input voltages V<sub>IN1</sub> = V<sub>IN2</sub> = 3.3 V using the typical application circuit (see Figure 20) unless otherwise noted.

| Characteristic                                                                                                                                                      | Symbol                | Min   | Тур  | Max   | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------|------|-------|------|

| LINEAR REGULATOR (LDO)                                                                                                                                              |                       |       |      |       | •    |

| LDO Output Voltage Range $V_{IN1}$ = $V_{IN2}$ = 2.8 V to 6.0 V, $I_{LDO}$ = 10 mA to 1000 mA                                                                       | V <sub>LDO</sub>      | 0.8   | _    | 5.0   | V    |

| LDO Feedback Voltage, LFB Pin Connected to LDO Pin $V_{\rm IN1}$ = $V_{\rm IN2}$ = 2.8 V to 6.0 V, $I_{\rm LDO}$ = 10 mA to 1000 mA. Includes Load Regulation Error | V <sub>LDO</sub>      | 0.784 | 0.8  | 0.816 | V    |

| LDO Voltage Margining Step Size                                                                                                                                     | $V_{MLDO}$            | -     | 1.0  | _     | %    |

| LDO Line Regulation<br>$V_{IN1} = V_{IN2} = 2.8 \text{ V to } 6.0 \text{ V}, I_{LDO} = 1000 \text{ mA}$                                                             | REG <sub>LNVLDO</sub> | -1.0  | _    | 1.0   | %    |

| LDO Load Regulation I <sub>LDO</sub> = 10 mA to 1000 mA                                                                                                             | REG <sub>LDVLDO</sub> | -1.0  | _    | 1.0   | %    |

| LDO Ripple Rejection, Dropout Voltage $V_{DO}$ = 1.0 V, $V_{RIPPLE}$ = +1.0 V p-p Sinusoidal, f = 300 kHz, $I_{LDO}$ = 500 mA                                       | V <sub>LDO_RR</sub>   | -     | 40   | _     | dB   |

| LDO Maximum Dropout Voltage (V <sub>IN</sub> - V <sub>LDO</sub> ) $V_{LDO} = 2.5 \text{ V, I}_{LDO} = 1000 \text{ mA}$                                              | V <sub>DO</sub>       | _     | -    | TBD   | ٧    |

| LDO Current Sense Comparator Threshold Voltage (V <sub>CS</sub> - V <sub>LDO</sub> )                                                                                | V <sub>CSTH</sub>     | 35    | 45   | 55    | mV   |

| LDO Pin Input Current                                                                                                                                               | I <sub>LDO</sub>      | 1.6   | 2.0  | 2.4   | mA   |

| LDO Feedback Input Current (LFB Pin)                                                                                                                                | I <sub>LFB</sub>      | -5.0  | -    | 5.0   | μА   |

| LDO Drive Output Current (LDRV Pin)                                                                                                                                 | I <sub>LDRV</sub>     | 2.0   | 3.6  | 5.0   | mA   |

| LDO Drive Current Limit (LDRV Pin)                                                                                                                                  | I <sub>DRLIM</sub>    | -     | 3.6  | -     | mA   |

| CS Pin Input Leakage Current V <sub>CS</sub> = 5.0 V                                                                                                                | I <sub>CSLK</sub>     | 50    | -    | 300   | μА   |

| LDO Error Amplifier Input Impedance (LFB Pin)                                                                                                                       | R <sub>IN</sub>       | -     | TBD  | _     | Ω    |

| LDO Error Amplifier Output Impedance (LCMP Pin)                                                                                                                     | R <sub>OUT</sub>      | -     | TBD  | -     | Ω    |

| LDO Pull-Down MOSFET Q4 Current Limit  T <sub>A</sub> = 25°C, V <sub>BST</sub> = 8.0 V (LDO Pin)                                                                    | I <sub>Q4_LIM</sub>   | -     | -2.0 | -     | А    |

| LDO Pull-Down MOSFET Q4 $R_{DS(ON)}$<br>$I_D = 1.0 \text{ A}, T_A = 25^{\circ}\text{C}, V_{BST} = 8.0 \text{ V}$                                                    | R <sub>DS(ON)</sub>   | -     | -    | 1.0   | Ω    |

| LDO Recommended Output Capacitance                                                                                                                                  | C <sub>LDO</sub>      | -     | 10   | _     | μF   |

| LDO Recommended Output Capacitor ESR                                                                                                                                | ESR <sub>CLDO</sub>   | -     | TBD  | -     | mΩ   |

| Thermal Shutdown (LDO Pull-Down FET Q4)                                                                                                                             | T <sub>SD</sub>       | 150   | 170  | 190   | °C   |

| Thermal Shutdown Hysteresis                                                                                                                                         | T <sub>SDHys</sub>    | _     | 15   | -     | °C   |

|                                                                                                                                                                     | 1                     |       | 1    | l .   | 1    |

#### STATIC ELECTRICAL CHARACTERISTICS (continued)

Characteristics noted under conditions -40°C  $\leq$  T<sub>J</sub> $\leq$  125°C unless otherwise noted. Input voltages V<sub>IN1</sub> = V<sub>IN2</sub> = 3.3 V using the typical application circuit (see Figure 20) unless otherwise noted.

| Characteristic                                                                                                                                   | Symbol               | Min  | Тур  | Max  | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------|------|------|------|

| CONTROL AND SUPERVISORY CIRCUITS                                                                                                                 |                      |      |      |      |      |

| Enable (EN1, EN2) Input Voltage Threshold                                                                                                        | V <sub>TH_EN</sub>   | 1.2  | 1.6  | 2.0  | V    |

| Enable (EN1, EN2) Input Voltage Threshold Hysteresis                                                                                             | V <sub>IHYS</sub>    | -    | 0.1  | _    | V    |

| Enable (EN1, EN2) Pull-Down Resistance                                                                                                           | R <sub>PU</sub>      | 30   | 60   | 120  | kΩ   |

| RESET Low-Level Output Voltage, I <sub>OL</sub> = 5.0 mA                                                                                         | V <sub>OL</sub>      | -    | _    | 0.4  | V    |

| RESET Leakage Current, OFF State, Pulled Up to 5.0 V                                                                                             | I <sub>LKG-RST</sub> | -    | -    | 10   | μА   |

| RESET Undervoltage Threshold on V <sub>OUT</sub> (ΔV <sub>OUT</sub> /V <sub>OUT)</sub> (Note 8)                                                  | V <sub>OUTITh</sub>  | -10  | -7.5 | -5.0 | %    |

| RESET Overvoltage Threshold on V <sub>OUT</sub> ( $\Delta$ V <sub>OUT</sub> /V <sub>OUT</sub> ) (Note 8)                                         | V <sub>OUTITh</sub>  | 5.0  | 7.5  | 10   | %    |

| $\overline{\text{RESET}} \text{ Undervoltage Threshold on V}_{\text{LDO}} (\Delta \text{V}_{\text{LDO}}/\text{V}_{\text{LDO}}) \text{ (Note 8)}$ | V <sub>LDOITh</sub>  | -10  | -7.5 | -5.0 | %    |

| RESET Overvoltage Threshold on V <sub>LDO</sub> (ΔV <sub>LDO</sub> /V <sub>LDO</sub> ) (Note 8)                                                  | V <sub>LDOITh</sub>  | 5.0  | 7.5  | 10   | %    |

| Reset Timer Voltage Threshold                                                                                                                    | V <sub>TH-RT</sub>   | TBD  | 1.2  | TBD  | V    |

| Reset Timer Source Current                                                                                                                       | I <sub>S-RT</sub>    | 20   | -    | 30   | mA   |

| Reset Timer Leakage Current                                                                                                                      | I <sub>LKG-RT</sub>  | -1.0 | _    | 1.0  | μА   |

| Reset Timer Saturation Voltage, Reset Timer Current = 300 μA                                                                                     | V <sub>SAT-RT</sub>  | -    | 100  | TBD  | mV   |

| Maximum Value of the Reset Timer Capacitor                                                                                                       | Ct                   | -    | _    | 47   | μF   |

| CLKSEL Threshold Voltage                                                                                                                         | V <sub>thCLKS</sub>  | 1.2  | 1.6  | 2.0  | V    |

| CLKSEL Pull-Up Resistance                                                                                                                        | R <sub>PU-CLKS</sub> | 60   | 120  | 240  | kΩ   |

| ADDR Threshold Voltage                                                                                                                           | V <sub>thADDR</sub>  | 1.2  | 1.6  | 2.0  | V    |

| ADDR Pull-Up Resistance                                                                                                                          | R <sub>PU-ADDR</sub> | 60   | 120  | 240  | kΩ   |

| SDA, SCL Pins I <sup>2</sup> C Bus (STANDARD)                                                                                                    | ,                    |      | •    | •    |      |

| Input Threshold Voltage                                                                                                                          | V <sub>Ith</sub>     | 1.3  | _    | 1.7  | V    |

| Input Voltage Threshold Hysteresis                                                                                                               | V <sub>IHYS</sub>    | -    | 0.2  | _    | V    |

| SDA, SCL Input Current, Input Voltage = 0.4 V to 6.0 V                                                                                           | I <sub>1</sub>       | -    | _    | 10   | μА   |

| SDA Low-Level Output Voltage, 3.0 mA Sink Current                                                                                                | V <sub>OL</sub>      | _    | _    | 0.4  | V    |

#### Notes

SCA, SCL Capacitance

8. This parameter does not include the tolerance of the external resistor divider.

pF

10

#### **DYNAMIC ELECTRICAL CHARACTERISTICS**

Characteristics noted under conditions -40°C  $\leq$  T<sub>J</sub> $\leq$  125°C unless otherwise noted. Input voltages V<sub>IN1</sub> = V<sub>IN2</sub> = 3.3 V using the typical application circuit (see Figure 20) unless otherwise noted.

| Characteristic                                                                                                                                                                 | Symbol              | Min | Тур | Max | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----|-----|-----|------|

| BUCK CONVERTER                                                                                                                                                                 |                     |     |     |     |      |

| Duty Cycle Range (Normal Operation)                                                                                                                                            | D                   | 0   | _   | 90  | %    |

| Switching Node SW Rise Time (Note 9) I <sub>LOAD</sub> = 3.0 A                                                                                                                 | t <sub>RISE</sub>   | -   | TBD | _   | ns   |

| Switching Node SW Fall Time (Note 9) I <sub>LOAD</sub> = 3.0 A                                                                                                                 | t <sub>FALL</sub>   | _   | TBD | _   | ns   |

| Maximum Deadtime (Note 9)                                                                                                                                                      | t <sub>D</sub>      | _   | TBD | -   | ns   |

| Buck Control Loop Propagation Delay (Note 9) $V_{INV} < 0.8 \text{ V to V}_{SW} > 90\% \text{ of High Level or V}_{INV} > 0.8 \text{ V to V}_{SW} < 10\% \text{ of Low Level}$ | t <sub>PD</sub>     | -   | 50  | -   | ns   |

| Soft Start Duration (Power Sequencing Disabled, EN1 = 1, EN2 = 1)                                                                                                              | t <sub>SS</sub>     | 200 | 350 | 800 | μS   |

| Fault Condition Timeout                                                                                                                                                        | t <sub>FAULT</sub>  | -   | 10  | -   | ms   |

| Retry Timer Cycle                                                                                                                                                              | t <sub>Ret</sub>    | _   | 100 | _   | ms   |

| OSCILLATOR                                                                                                                                                                     |                     | I   |     |     |      |

| Oscillator Default Frequency (Switching Frequency), FREQ Pin Open                                                                                                              | f <sub>OSC</sub>    | 270 | 300 | 330 | kHz  |

| Oscillator Frequency Range                                                                                                                                                     | f <sub>OSC</sub>    | 200 |     | 400 | kHz  |

| Oscillator Frequency Accuracy $R_{\text{F}} = 100 \text{ k}\Omega$                                                                                                             | f <sub>osc</sub>    | 360 | 400 | 440 | kHz  |

| Oscillator Frequency Accuracy $R_{\text{F}} = 200 \text{ k}\Omega$                                                                                                             | fosc                | 180 | 200 | 220 | kHz  |

| Oscillator Output Signal Duty Cycle (Square Wave, 180° Out-of-Phase with the Internal Suitable Oscillator)                                                                     | D <sub>OSC</sub>    | -   | 50  | ı   | %    |

| Synchronization Pulse Minimum Duration                                                                                                                                         | t <sub>SYNC</sub>   | 300 | _   | -   | ns   |

| BOOST REGULATOR                                                                                                                                                                |                     |     |     |     |      |

| Boost Regulator FET Maximum ON Time                                                                                                                                            | t <sub>ON</sub>     | _   | 24  | _   | μS   |

| Boost Regulator Control Loop Propagation Delay (Note 9)                                                                                                                        | t <sub>BST_PD</sub> | -   | 50  | -   | ns   |

| Boost Switching Node V <sub>BD</sub> Rise Time (Note 9) $I_{BST} = 20 \text{ mA}$                                                                                              | t <sub>B_RISE</sub> | -   | 15  | 40  | ns   |

| Boost Switching Node V <sub>BD</sub> Fall Time (Note 9)                                                                                                                        | t <sub>B_FALL</sub> |     |     |     | ns   |

#### Notes

9. Design Information only. Not production tested.

#### **DYNAMIC ELECTRICAL CHARACTERISTICS (continued)**

Characteristics noted under conditions -40°C  $\leq$  T<sub>J</sub> $\leq$  125°C unless otherwise noted. Input voltages V<sub>IN1</sub> = V<sub>IN2</sub> = 3.3 V using the typical application circuit (see Figure 20) unless otherwise noted.

| Characteristic                                                                                           | Symbol              | Min | Тур | Max | Unit  |

|----------------------------------------------------------------------------------------------------------|---------------------|-----|-----|-----|-------|

| LINEAR REGULATOR (LDO)                                                                                   |                     | 1   |     |     | •     |

| LDO Output Current Slew Rate                                                                             | I <sub>SR</sub>     | _   | TBD | _   | mA/μs |

| Fault Condition Timeout                                                                                  | t <sub>FAULT</sub>  | -   | 1.0 | _   | ms    |

| Retry Timer Cycle                                                                                        | t <sub>Ret</sub>    | -   | 100 | -   | ms    |

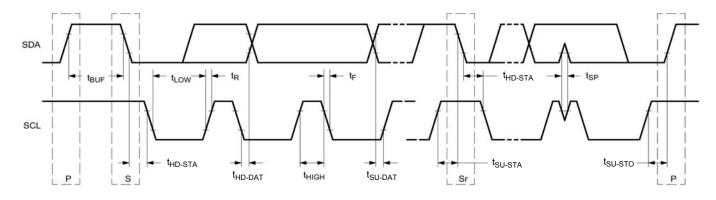

| SCA, SCL PIN, I <sup>2</sup> C BUS (STANDARD)                                                            |                     |     |     |     | •     |

| SCL Clock Frequency                                                                                      | f <sub>SCL</sub>    | 0   | _   | 100 | kHz   |

| Bus Free Time Between a STOP and a START Condition                                                       | t <sub>BUF</sub>    | 4.7 | _   | -   | μS    |

| Hold Time (Repeated) START Condition (After this period, the first clock pulse is generated.)            | t <sub>HD-STA</sub> | 4.0 | _   | _   | μS    |

| Low Period of the SCL Clock                                                                              | t <sub>LOW</sub>    | 4.7 | _   | _   | μS    |

| High Period of the SCL Clock                                                                             | t <sub>HIGH</sub>   | 4.0 | _   | _   | μS    |

| SDA Fall Time from $V_{IH\_MAX}$ to $V_{IL\_MIN}$ . Bus Capacitance 10 pF to 400 pF, 3.0 mA Sink Current | t <sub>F</sub>      | _   | _   | 250 | ns    |

| Setup Time for a Repeated START Condition                                                                | t <sub>SU-STA</sub> | 4.7 | -   | -   | μS    |

| Data Hold Time for I <sup>2</sup> C bus devices (Note 10), (Note 11)                                     | t <sub>HD-DAT</sub> | 0   | -   | -   | μS    |

| Data Setup Time                                                                                          | t <sub>SU-DAT</sub> | 250 | _   | _   | ns    |

| Setup Time for STOP Condition                                                                            | t <sub>su-sto</sub> | 4.0 | _   | _   | μS    |

#### Notes

10. Design Information only. Not production tested.

Capacitive Load for Each Bus Line

11. The device provides an internal hold time of at least 300 ns for the SDA signal (refer to the V<sub>IH\_MIN</sub> of the SCL signal) to bridge the undefined region of the falling edge of SCL.

$\mathsf{C}_\mathsf{B}$

# **Timing Diagram**

Figure 2. Definition of Time on the I<sup>2</sup>C Bus

400

рF

### **Electrical Performance Curves**

|                                              | J L                               |

|----------------------------------------------|-----------------------------------|

| Figure 3. Buck R <sub>DS(ON)</sub> (Temp)    | Figure 6. I <sub>LIM</sub> (Temp) |

|                                              | 1                                 |

|                                              |                                   |

|                                              |                                   |

|                                              |                                   |

|                                              |                                   |

|                                              |                                   |

|                                              |                                   |

|                                              |                                   |

|                                              |                                   |

|                                              |                                   |

|                                              |                                   |

|                                              |                                   |

|                                              |                                   |

| Figure 4. F <sub>OSC</sub> (R <sub>F</sub> ) | Figure 7. Vref (Temp)             |

| 1.3a.a 11.08C (.4r)                          | rigule 7. Viel (Tellip)           |

|                                              |                                   |

|                                              |                                   |

|                                              |                                   |

|                                              |                                   |

|                                              |                                   |

|                                              |                                   |

|                                              |                                   |

|                                              |                                   |

|                                              |                                   |

|                                              |                                   |

|                                              |                                   |

|                                              |                                   |

Figure 5. Buck Efficiency

Figure 8. RT Timer (R<sub>t</sub>, C<sub>t</sub>)

#### SYSTEM/APPLICATION INFORMATION

#### INTRODUCTION

The 33702 power supply integrated circuit provides the means to efficiently supply the Power QUICC and other families of Motorola microprocessors. It incorporates a high-performance synchronous buck regulator, supplying the microprocessor's core, and a low dropout (LDO) linear regulator providing the microprocessor I/O and bus voltages.

This device incorporates many advanced features; e.g., precisely maintained up/down power sequencing, ensuring the proper operation and protection of the CPU and power system. At the same time, it provides high flexibility of configuration, allowing the maximum optimization of the power supply system.

#### **FUNCTIONAL DESCRIPTION**

#### **Switching Regulator**

The switching regulator is a high-frequency (300 kHz default, adjustable in the range from 200 kHz to 400 kHz), synchronous buck converter driving integrated high-side and low-side N-channel power MOSFETs. The switching regulator output voltage is adjustable by means of an external resistor divider to provide the required output voltage within plus/minus two percent accuracy, and it is intended to directly power the core of the microprocessor. The buck controller utilizes a Sensorless PWM Current Mode Control topology to achieve excellent line rejection, stabilize the feedback loop, and provide cycle-by-cycle current limiting.

A typical bootstrap technique is used to provide voltage necessary to properly enhance the high-side MOSFET gate. When the regulator is supplied only from low-input voltage (e.g., single +3.3 V supply rail), the bootstrap capacitor is charged from the internal boost regulator output  $V_{BST}$  through an external diode. This arrangement allows the 33702 to operate from very low input voltage and also comply with the power sequencing requirements of the supplied microcontroller.

To avoid destruction of the supplied circuits, a current limit with retry capability was implemented in the switching regulator. When an overcurrent condition occurs and the switch current reaches the peak current limit value, the main (high-side) switch is turned off until the inductor current decays to the valley value, which is one-half of the peak current limit. If an overcurrent condition exists for 10 ms, the buck regulator control circuit shuts the switcher OFF and the switcher retry timer starts to time out. When the timer expires after 100 ms, the switcher engages the start-up sequence and runs for 10 ms, repeatedly checking for the overcurrent condition. During the current limited operation (e.g., in case of short circuit on the switching regulator output), the switching regulator operation is not synchronized to the oscillator frequency.

The output voltage  $V_{OUT}$  can be adjusted by means of an external resistor divider connected to the feedback control pin INV. The switching regulator output voltage can be adjusted in the range of 0.8 V to 5.0 V, but the  $V_{OUT}$  output voltage is always lower than the input voltage to the regulator. Power-up, power-down, and fault management are coordinated with the linear regulator.

#### Thermal Shutdown

To increase the overall safety of the system designed with the 33702, an internal thermal shutdown function has been incorporated into the switching regulator circuit. The 33702 senses the temperature of the buck regulator main switching FET (high-side FET Q1; see Figure 1), the low-side (synchronous FET Q2), and control circuit. If the temperature of any of the monitored components exceeds the limit of safe operation (thermal shutdown), the switching regulator will be shut down. After the temperature falls below the value given by the thermal shutdown hysteresis window, the switcher will retry to operate again.

The  $V_{OUT}$  pull-down FET Q3 has an independent thermal shutdown control. When the Q3 temperature exceeds the thermal shutdown limit, the Q3 will be turned off without affecting the switcher operation.

#### Soft Start

A switching regulator soft start feature is incorporated in the 33702. The soft start is active each time the IC is enabled,  $V_{\text{IN}}$  is reapplied, or after a fault retry. Other transient events do not activate the soft start.

#### **Boost Regulator**

A boost regulator provides a high voltage necessary to properly drive the buck regulator power MOSFETs, especially during the low input voltage condition. The LDO regulator external N-channel MOSFET gate is also powered from the boost regulator. In order to properly enhance the high-side MOSFETs when only a +3.3 V supply rail powers the integrated circuit, the boost regulator provides an output voltage of 8.0 V nominal value.

The 33702 boost regulator uses a simple hysteretic current control technique, which allows fast power-up and does not require any compensation. When the boost regulator main power switch (low side) is turned on, the current in the inductor starts to ramp up. After the inductor current reaches the upper current limit (nominally set at 1.0 A), the low-side switch is turned off and the current charges the output capacitor through the internal rectifier. When the inductor current falls below the valley current limit value (nominally 600 mA), the low-side switch is turned on again, starting the next switching cycle. After

the boost regulator output capacitor reaches its regulation limit, the low-side switch is turned off until the output voltage falls below the regulation limit again.

#### Oscillator

A 300 kHz (default) oscillator sets the switching frequency of the buck regulator. The frequency of the oscillator can be adjusted between 200 kHz and 400 kHz by an optional external resistor  $R_{\rm F}$  connected from the FREQ pin of the integrated circuit to ground. See Figure 4 for frequency resistor selection.

The CLKSYN pin can be configured either as an oscillator output when the CLKSEL pin is left open or it can be used as a synchronization input when the CLKSEL pin is grounded. The oscillator output signal is a square wave logic signal with 50 percent duty cycle, 180 degrees out-of-phase with the internal clock signal. This allows opposite phase synchronization of two 3370x devices.

When the CLKSYN pin is used as synchronization input (CLKSEL pin grounded), the external resistor  $\rm R_F$  chosen from the chart in Figure 4 should be used to synchronize the internal slope compensation ramp to the external clock. Operation is only recommended between 200 kHz and 400 kHz. The supplied synchronization signal does not need to be 50 percent duty cycle. Minimum pulse width is 300 ns.

#### Low Dropout Linear Regulator (LDO)

The adjustable low dropout linear regulator (LDO) is capable of supplying a 1.0 A output current. It has a current limit with retry capability. When the voltage measured across the current sense resistor reaches the 45 mV threshold, the control circuit limits the current for 1.0 ms and if the overcurrent condition still exists the linear regulator is turned off. At the same time the overcurrent condition is detected, the Retry Timer starts to time out. When the timer expires after 100 ms, the LDO tries to power up again for 1.0 ms, repeatedly checking for the overcurrent condition. The current limit of the LDO can be set by using the following formula:

$$I_{LIM}$$

= 45 mV/R<sub>S</sub>

Where  $R_S$  is the LDO current sense resistor, connected between the CS pin and the LDO pin output (see Figure 20).

When no current sense resistor is used, it is still possible to detect the overcurrent condition by tying the current sense pin CS to the  $V_{BST}$  voltage. In this case, the overcurrent condition is sensed by saturation of the linear regulator driver buffer.

The output voltage of the LDO can be adjusted by means of an external resistor divider connected to the feedback control pin LFB. The linear regulator output voltage can be adjusted in the range of 0.8 V to 5.0 V, but the LDO output voltage is always lower than the input voltage to the regulator. Power-up, power-down, and fault management are coordinated with the switching regulator.

#### Thermal Shutdown

The LDO pull-down FET Q4 has an independent thermal shutdown control. When the Q4 temperature exceeds the

thermal shutdown limit, the Q4 will be turned off without affecting the LDO operation.

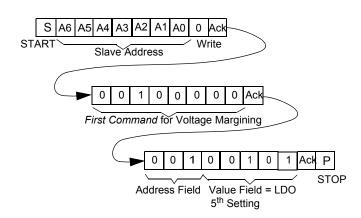

#### **Voltage Margining**

The 33702 includes a voltage margining feature accessed through the  $I^2C$  bus. Voltage margining allows for independent adjustment of the Switcher  $V_{OUT}$  voltage and the linear output  $V_{LDO}.$  Each can be adjusted up and down in 1% steps to a range of  $\pm 7\%.$  This feature allows for worst case system validation; i.e., determining the design margin. Margining details are described in the section entitled  $I^2C$  Bus Operation, beginning on page 19 of this datasheet.

#### **RESET**

The  $\overline{\text{RESET}}$  pin is an open drain output. The Reset Control circuit supervises both output voltages—the linear regulator output  $V_{LDO}$  and the switching regulator output  $V_{OUT}$ . When either of these two regulators is out of regulation (high or low), the  $\overline{\text{RESET}}$  pin is pulled low. There is a 20  $\mu s$  delay filter preventing erroneous resets. During power-up sequencing,  $\overline{\text{RESET}}$  is held low until the Reset Timer times out.

#### Reset Timer Power-Up Delay (RT)

The Reset Timer Power-Up Delay (RT) pin is used to set the delay between the time when the LDO and switcher outputs are active and stable and the release of the RESET output. An external resistor and capacitor are used to program the timer. The power-up delay can be obtained by using the following formula:

$$T_D = 10 \text{ ms} + R_t C_t$$

Where  $R_t$  is the Reset Timer programming resistor and  $C_t$  is the Reset Timer programming capacitor, both connected in parallel from RT to ground.

Note Observe the maximum  $C_t$  value and expect reduced accuracy if  $R_t$  is less than 10 k $\Omega$ .

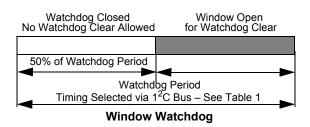

#### Watchdog Timer

A watchdog function is available via I<sup>2</sup>C bus communication. It is possible to select either window watchdog or time-out watchdog operation, as illustrated in Figure 9 on page 15.

Watchdog time-out starts when the watchdog function is activated via I<sup>2</sup>C bus sending a Watchdog Programming command byte, thus determining watchdog operation (window or time-out) and period duration (refer to Table 1, page 15). If the watchdog is cleared by receiving a new Watchdog Programming command through the I<sup>2</sup>C bus, the watchdog timer is reset and the new time-out period begins. If the watchdog time expires, the RESET will become active (LOW) for a time determined by the RC components of the RT timer plus 10 ms. After a watchdog time-out, the function is no longer active.

Window Open for Watchdog Clear

Figure 9. Watchdog Operation

Table 1. Watchdog Programming Command Byte (as a 2nd Command Byte)

| Address |   |   |   | ١ | /alu | е | Action |                      |

|---------|---|---|---|---|------|---|--------|----------------------|

| 0       | 1 | 1 | 0 | 0 | 0    | 0 | 0      | 1st Command          |

| 0       | 1 | 1 | 0 | 0 | 0    | 0 | 0      | WD OFF<br>(Note 12)  |

| 0       | 1 | 1 | 0 | 1 | 0    | 0 | 0      | WD 1280 ms<br>WinOFF |

| 0       | 1 | 1 | 0 | 1 | 0    | 0 | 1      | WD 320 ms<br>WinOFF  |

| 0       | 1 | 1 | 0 | 1 | 0    | 1 | 0      | WD 80 ms<br>WinOFF   |

| 0       | 1 | 1 | 0 | 1 | 0    | 1 | 1      | WD 20 ms<br>WinOFF   |

| 0       | 1 | 1 | 0 | 1 | 1    | 0 | 0      | WD 1280 ms<br>WinON  |

| 0       | 1 | 1 | 0 | 1 | 1    | 0 | 1      | WD 320 ms<br>WinON   |

| 0       | 1 | 1 | 0 | 1 | 1    | 1 | 0      | WD 80 ms<br>WinON    |

| 0       | 1 | 1 | 0 | 1 | 1    | 1 | 1      | WD 20 ms<br>WinON    |

#### Notes

The Watchdog feature will be turned ON automatically after receiving any other valid command byte changing watchdog time.

When the Window Watchdog function is selected, the timer cannot be cleared during the Closed Window time, which is 50% of the total watchdog period. When the watchdog is cleared, the timer is reset and starts a new time-out period. If the watchdog is not cleared during the Open Window time, the RESET will become active (LOW) for a time determined by the RC components of the RT timer plus 10 ms.

#### **EN1 and EN2 Control Pins**

These two pins permit positive logic control of the Enable function and selection of the Power Sequencing mode concurrently. Table 2 depicts the EN1 and EN2 function and Power Sequencing mode selection.

Both EN1 and EN2 pins have internal pull-down resistors and both can withstand a short circuit to the supply voltage, 6.0 V.

**Table 2. Operating Mode Selection**

| EN1 | EN2 | Operating Mode                             |

|-----|-----|--------------------------------------------|

| 0   | 0   | Regulators Disabled                        |

| 0   | 1   | Standard Power Sequencing                  |

| 1   | 0   | Inverted Power Sequencing                  |

| 1   | 1   | Regulators Enabled,<br>No Power Sequencing |

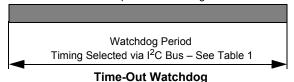

#### **Power Sequencing Modes**

The power sequencing of the two outputs of this power supply IC is in compliance with the Motorola Power QUICC and other 32-bit microprocessor requirements. When the input voltage is applied, the switcher and linear regulator outputs follow the supply rail voltage during power-up and power-down in the limits given by the microcontroller power sequencing specification, illustrated in Figures 10 through 12. There are two possible power sequencing modes, Standard and Inverted, as explained in more detail below. The third mode of operation is Power Sequencing Disabled.

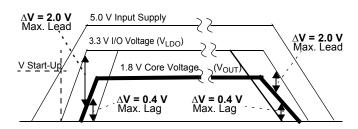

Figure 10. Standard Power Up/Down Sequence in +3.3 V Supply System

Figure 11. Standard Power Up/Down Sequence in +5.0 V Supply System

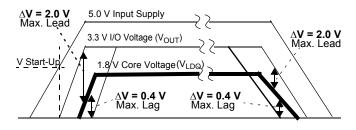

Figure 12. Inverted Power Up/Down Sequence in +5.0 V Supply System

#### **Standard Power Sequencing**

When the power supply IC operates in the Standard Power Sequencing mode, the switcher output provides the core voltage for the microprocessor. This situation and operating conditions are illustrated in Figure 10 and Figure 11. Table 2, page 15, shows the Power Sequencing mode selection.

#### **Inverted Power Sequencing**

When the power supply IC is operating in the Inverted Power Sequencing mode, the linear regulator (LDO) output provides the core voltage for the microprocessor, as illustrated in Figure 12. Table 2 shows the Power Sequencing mode selection.

#### 33702 POWER SEQUENCING

#### Requirements

- I/O supply voltage not to exceed core voltage by more than 2.0 V.

- Core supply voltage not to exceed I/O voltage by more than 0.4 V.

#### **Methods of Control**

The 33702 has several methods of monitoring and controlling the regulator output voltages, as described in the paragraphs below. Power sequencing control is also achieved through the intrinsic operation of the regulators. The EN1 and EN2 pins can be used to disable the power sequencing (refer to Table 2, page 15.

#### **Intrinsic Operation**

For both the LDO and switcher, whenever the output voltage is below the regulation point, the LDO external Pass FET will be on or the Buck High-Side FET will be on at a duty cycle controlled by the switcher. Because these devices are FETs, current can flow in either direction, balancing the voltages via the common supply pin. The ability to maintain the FETs on will depend on the available gate voltage, and thus the size of the boost regulator storage capacitor.

#### **Standard Power Sequencing Control**

Comparators monitor voltage differences between the LDO (LDO pin) and the switcher ( $V_{OLIT}$  pin) outputs as follows:

- LDO > V<sub>OUT</sub> + 1.8 V, turn off LDO. The LDO can be forced off. This occurs whenever the LDO output voltage exceeds the switcher output voltage by more than 1.8 V.

- 2.  $LDO > V_{OUT} + 1.9 \ V$ , shunt LDO to ground. If turning off the LDO is insufficient and the LDO output voltage exceeds the switcher output voltage by more than 1.9 V, a 1.0  $\Omega$  shunt FET is turned on that discharges the LDO load capacitor to ground. The shunt FET is used for switcher output shorts to ground and for power down in case of  $V_{IN1} \neq V_{IN2}$  with the switcher output falling faster than the LDO.

- LDO < V<sub>OUT</sub> + 1.7 V, cancel (1) and (2) above, re-enable LDO. Normal operation resumes when the LDO output voltage is less than 1.7 V above the switcher output voltage.

- LDO < V<sub>OUT</sub> 0.2 V, turn off switcher. The switcher can be forced off. This occurs whenever the LDO is less than V<sub>OUT</sub> - 0.2 V.

- 5.  $LDO < V_{OUT} 0.3 V$ , turn on Sync (LS) FET and 1.0  $\Omega$   $V_{OUT}$  sink FET. The Buck High-Side FET is forced off and the Sync FET is forced on. This occurs when the switcher output voltage exceeds the LDO output by more than 300 mV

- 6. LDO > V<sub>OUT</sub>, reset (4) and (5) above. Normal operation resumes when LDO > V<sub>OUT</sub>.

#### **Inverted Power Sequencing Control**

Comparators monitor voltage differences between the switcher (V<sub>OUT</sub> pin) and LDO (LDO pin) outputs as follows:

- V<sub>OUT</sub> > LDO + 1.8 V, turn off V<sub>OUT</sub>. The switcher V<sub>OUT</sub> can be forced off. This occurs whenever the V<sub>OUT</sub> output voltage exceeds the LDO output voltage by more than 1.8 V.

- V<sub>OUT</sub> > LDO + 1.9 V, shunt V<sub>OUT</sub> to ground. If turning off

the switcher V<sub>OUT</sub> is insufficient and the V<sub>OUT</sub> output

voltage exceeds the LDO output voltage by more than

1.9 V, a 1.0 Ω shunt FET is turned on that discharges the

V<sub>OUT</sub> load capacitor to ground. The shunt FET is used for

LDO output shorts to ground and for power-down in case

of V<sub>IN1</sub> ≠ V<sub>IN2</sub> with LDO output falling faster than the

V<sub>OUT</sub>.

- V<sub>OUT</sub> < LDO + 1.7 V, cancel (1) and (2) above, re-enable V<sub>OUT</sub>. Normal operation resumes when the V<sub>OUT</sub> output voltage is less than 1.7 V above the LDO output voltage.

- 4.  $V_{OUT}$  < LDO 0.2 V, turn off LDO. The LDO can be forced off. This occurs whenever the  $V_{OUT}$  is less than  $V_{LDO}$  0.2 V.

- V<sub>OUT</sub> < LDO 0.3 V, turn on the 1.0 Ω LDO sink FET.

<p>This occurs when the LDO output voltage exceeds the V<sub>OUT</sub> output by more than 300 mV.

- V<sub>OUT</sub> > LDO, reset (4) and (5) above. Normal operation resumes when V<sub>OUT</sub> > LDO.

#### **Standard Operating Mode**

#### 1. Single 3.3 V Supply, $V_{IN} = V_{IN1} = V_{IN2} = 3.3 V$

The 3.3 V supplies the microprocessor I/O voltage, the switcher supplies core voltage (e.g., 1.8 V nominal), and the LDO operates independently (see Figure 10, page 15). Power sequencing depends only on the normal switcher intrinsic operation to control the Buck High-Side FET.

#### Power Up

When  $V_{IN}$  is rising, initially  $V_{OUT}$  will be below the regulation point and the Buck High-Side FET will be on. In order not to exceed the 2.0 V differential requirement between the I/O  $(V_{IN})$  and the core  $(V_{OUT})$ , the switcher must start up at 2.0 V or less and be able to maintain the 2.0 V or less differential. The maximum slew rate for  $V_{IN}$  is 1.0 V/ms.

#### **Power Down**

When  $V_{IN}$  is falling,  $V_{OUT}$  will be below the regulation point; therefore the Buck High-Side FET will be on. In the case where  $V_{OUT}$  is falling faster than  $V_{IN}$ , the Buck High-Side FET will attempt to maintain  $V_{OUT}$ . In the case where  $V_{IN}$  is falling faster

than  $V_{OUT}$ , the Buck High-Side FET is also on, and the  $V_{OUT}$  load capacitor will be discharged through the Buck High-Side FET to  $V_{IN}$ . Thus, provided  $V_{IN}$  does not fall too fast, the core voltage ( $V_{OUT}$ ) will not exceed the I/O voltage ( $V_{IN}$ ) by more than a maximum of 0.4 V.

#### Shorted Load

- V<sub>OUT</sub> shorted to ground. This will cause the I/O voltage to exceed the core voltage by more than 2.0 V. No load protection.

- V<sub>IN</sub> shorted to ground. Until the switcher load capacitance is discharged, the core voltage will exceed the I/O voltage by more than 0.4 V. By the intrinsic operation of the switcher, the load capacitor will be discharged rapidly through the Buck High-Side FET to V<sub>IN</sub>.

- V<sub>OUT</sub> shorted to supply. No load protection. 33702 protected by current limit and thermal limit.

# 2. Single 5.0 V Supply, $V_{IN1} = V_{IN2}$ , or Dual Supply $V_{IN1} \neq V_{IN2}$

The LDO supplies the microprocessor I/O voltage. The switcher supplies the core (e.g., 1.8 V nominal) (see Figure 11, page 15).

#### Power Up

This condition depends upon the regulator current limit, load current and capacitance, and the relative rise times of the  $V_{IN1}$  and  $V_{IN2}$  supplies. There are 2 cases:

- LDO rises faster than V<sub>OUT</sub>. The LDO uses control methods (1) and (2) described in the Methods of Control section, page 16.

- V<sub>OUT</sub> rises faster than LDO. The switcher uses control methods (4) and (5) described in the Methods of Control section, page 16.

#### **Power Down**

This condition depends upon the regulator load current and capacitance and the relative fall times of the  $V_{\text{IN1}}$  and  $V_{\text{IN2}}$  supplies. There are 2 cases:

V<sub>OUT</sub> falls faster than LDO. The LDO uses control methods (1) and (2) described in the Methods of Control section, page 16.

In the case  $V_{IN1} = V_{IN2}$ , the intrinsic operation will turn on both the Buck High-Side FET and the LDO external Pass FET, and will discharge the LDO load capacitor into the  $V_{IN}$  supply.

LDO falls faster than V<sub>OUT</sub>. The switcher uses control methods (4) and (5) described in the Methods of Control section, page 16.

#### Shorted Load

- V<sub>OUT</sub> shorted to ground. The LDO uses method (1) and

described in the Methods of Control section, page 16.

- LDO shorted to ground. The switcher uses control

methods (4) and (5) described in the Methods of Control

section, page 16.

- 3. *V<sub>IN1</sub>* shorted to ground. This is equivalent to the LDO output shorted to ground.

- V<sub>IN2</sub> shorted to ground. This is equivalent to the switcher output shorted to ground.

- V<sub>OUT</sub> shorted to supply. No load protection. 33702 protected by current limit and thermal limit.

- 6. *LDO shorted to supply.* No load protection. 33702 protected by current limit and thermal limit.

#### **Inverted Operating Mode**

#### 1. Single 3.3 V Supply, $V_{IN} = V_{IN1} = V_{IN2} = 3.3 V$

The 3.3 V supplies the microprocessor I/O voltage, the LDO supplies core voltage (e.g., 1.8 V nominal), and the switcher  $V_{OUT}$  operates independently. Power sequencing depends only on the normal LDO intrinsic operation to control the Pass FET.

#### Power Up

When  $V_{IN}$  is rising, initially LDO will be below the regulation point and the Pass FET will be on. In order not to exceed the 2.0 V differential requirement between the I/O ( $V_{IN}$ ) and the core (LDO), the LDO must start up at 2.0 V or less and be able to maintain the 2.0 V or less differential. The maximum slew rate for  $V_{IN}$  is 1.0 V/ms.

#### **Power Down**

When  $V_{IN}$  is falling, LDO will be below the regulation point; therefore the Pass FET will be on. In the case where LDO is falling faster than  $V_{IN}$ , the Pass FET will attempt to maintain LDO. In the case where  $V_{IN}$  is falling faster than LDO, the Pass FET is also on, and the LDO load capacitor will be discharged through the Pass FET to  $V_{IN}$ . Thus, provided  $V_{IN}$  does not fall too fast, the core voltage (LDO) will not exceed the I/O voltage  $(V_{IN})$  by more than maximum of 0.4 V.

#### Shorted Load

- LDO shorted to ground. This will cause the I/O voltage to exceed the core voltage by more than 2.0 V. No load protection.

- V<sub>IN</sub> shorted to ground. Until the LDO load capacitance is discharged, the core voltage will exceed the I/O voltage by more than 0.4 V. By the intrinsic operation of the LDO,

- the load capacitor will be discharged rapidly through the Pass FET to  $V_{\rm IN}$ .

- 3. LDO shorted to supply. No load protection.

# 2. Single 5.0 V Supply, $V_{IN1} = V_{IN2}$ , or Dual Supply $V_{IN1} \neq V_{IN2}$

The switcher  $V_{OUT}$  supplies the microprocessor I/O voltage. The LDO supplies the core (e.g., 1.8 V nominal) (see Figure 12, page 16).

#### Power Up

This condition depends upon the regulator current limit, load current and capacitance, and the relative rise times of the  $V_{IN1}$  and  $V_{IN2}$  supplies. There are 2 cases:

- V<sub>OUT</sub> rises faster than LDO. The switcher V<sub>OUT</sub> uses control methods (4) and (5) described in the Methods of Control section, page 17.

- LDO rises faster than V<sub>OUT</sub>. The LDO uses control methods (1) and (2) described in the Methods of Control section, page 17.

#### **Power Down**

This condition depends upon the regulator load current and capacitance and the relative fall times of the  $V_{\text{IN1}}$  and  $V_{\text{IN2}}$  supplies. There are 2 cases:

LDO falls faster than V<sub>OUT</sub>. The V<sub>OUT</sub> uses control methods (4) and (5) described in the Methods of Control section, page 17.

In the case  $V_{IN1}$  =  $V_{IN2}$  the intrinsic operation will turn both the Buck High-Side FET and the LDO external Pass FET, and will discharge the  $V_{OUT}$  load capacitor into the  $V_{IN}$  supply.

V<sub>OUT</sub> falls faster than LDO. The LDO uses control methods (1) and (2) described in the Methods of Control section, page 17.

#### Shorted Load

- LDO shorted to ground. The V<sub>OUT</sub> uses methods (4) and (5) described in the Methods of Control section, page 17.

- V<sub>OUT</sub> shorted to ground. The LDO uses control methods

and (2) described in the Methods of Control section.

- 3. *V<sub>IN1</sub>* shorted to ground. This is equivalent to the LDO output shorted to ground.

- V<sub>IN2</sub> shorted to ground. This is equivalent to the switcher V<sub>OUT</sub> output shorted to ground.

- 5. LDO shorted to supply. No load protection.

- V<sub>OUT</sub> shorted to supply. No load protection. 33702 protected by current limit and thermal limit.

#### I<sup>2</sup>C BUS OPERATION

#### Introduction

The 33702 device is compatible with the  $I^2C$  interface standard. SDA and SCL pins are the Serial Data and Serial Clock pins of the  $I^2C$  bus.

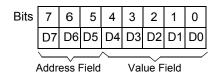

#### I<sup>2</sup>C Command and Data Formats

#### **Communication Start**

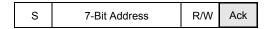

Communication starts with a START condition, followed by the slave device unique address. Figure 13 illustrates the data transfer beginning an I<sup>2</sup>C communication for a 7-bit slave address.

Figure 13. Communication Using 7-Bit Address

#### **Slave Address Definition**